|

|

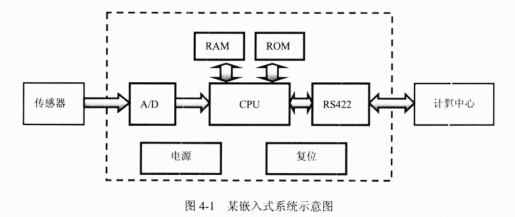

某公司负责研制一个嵌入式计算机系统,如图4-1所示。该系统以PowerPC处理器为核心,通过AD进行实时数据采集,并将采集来的数据进行预处理后,通过RS422总线发送给后端计算中心。

同时为了提高产品的安全性和可靠性,设计实现了机内自测试(Built_In_Test,BIT)。BIT依靠自身电路和程序完成对计算机平台硬件的功能检查、故障诊断与隔离。

|

|

|

问题:1.1

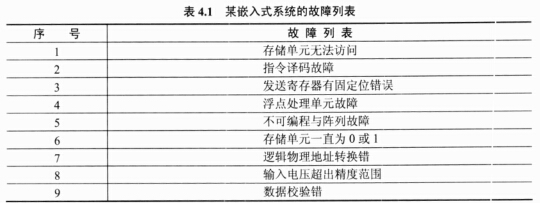

王工负责对该系统进行故障模式分析,识别出了该系统可能出现的故障模式,如表4.1所示。请将属于CPU和RAM的故障填写在答题纸的对应栏中。

|

|

|

问题:1.3

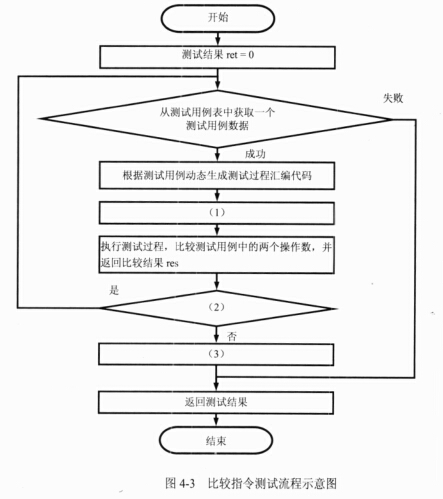

李工负责设计CPU单元的BIT测试算法,通过对每组指令分别设计一组测试用例,定义不同的操作数、操作码和预期值,在指令运行后比较结果与预期值。由于该系统选用的处理器集成了多级Cache(高速缓存),并且指令缓存和数据缓存是分开K,执行指令功能测试前需要刷新指令Cache,以保证与内存中的测试代码一致。每个测试项的测试结果正确为0,故障为1。

以32位字比较指令cmpw测试为例,cmpw将寄存器rA和rB内数据比较的结果(大于、小于、等于)放入条件寄存器cdc,其操作码为0x7C000000,测试用例数据如表4.2所示。

cmpw指令功能测试的算法流程示意如图4-3所示。请补全流程图4-3中的执行操作,将答案填写在答题纸的对应栏中。

|

|

|

|

|