|

|

阅读以下说明,回答问题1至问题4。

【说明】

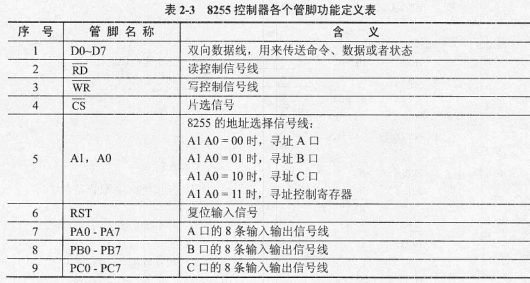

王工在采用某16位嵌入式CPU进行A/D采集硬件电路设计时,利用8255控制器C口中的PC0输出控制信号,利用PC7读入AD574的状态信号,利用A口和B口读入AD574转换好的12位数据。图2-1为该A/D采集硬件系统设计的部分连接示意图。

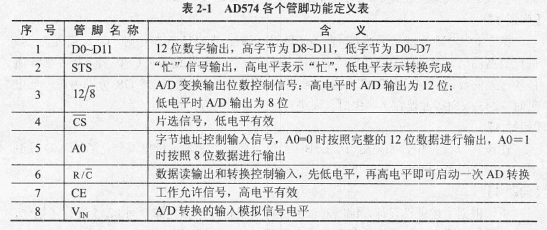

其中,AD574各个管脚功能定义如表2-1所述。

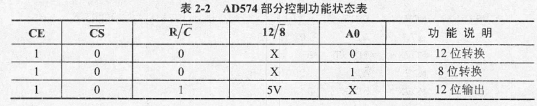

AD574的控制功能状态表如表2-2所示。

8255控制器各个管脚及地址控制描述如表2-3所示。

|

|

|

|

问题:2.1

在该嵌入式系统设计中,AD574是工作在12位转换模式还是8位转换模式?

|

|

|

|

问题:2.3

在该A/D变换中,如果用1/2LSB(最低有效位)来表示量化误差,当该A/D控制器的量程范围为5V时,其量化误差是多大?

|

|

|

|

|

|